So you’re on the hunt for a new memory kit, and whilst you know that “lower = better”.. you don’t exactly know why. You may even know the name “CAS Latency” .. but what is that, exactly? Why is it better to have CL8 over CL10? What are all these other numbers? What do the abbreviations mean? Why is it all so complicated!? Oh, and why do I care? Well.. read on, find out, and rejoice! I’m here to save the day.

CAS Latency

Aka CL

Example timing: 9-10-11-24 2

Highlighted in bold is your CAS Latency. This is the delay time in which the memory a) receives a command from the processor, to the point where it b) sends data back to the processor. It is fairly obvious why this is regarded as the most important timing when it comes down to it. Memory with a CL of 7 will respond faster than memory with a CL of 9.

RAS to CAS Delay

Aka tRCD

Example timing: 9-10-11-24-2

Simple explanation: The time between accessing a row of data, and then accessing the related column of data. RAS to CAS delay has a lesser important delay on performance than CL.

More complicated explanation:

Each data storage location is arranged in a grid (the correct term is matrix). Think of a memory chip as a game of Battleship. If you are trying to access the data stored on location “H7”, tRCD is the time between the memory accessing “Row H” (RAS: Row Address Strobe) and the memory accessing “column 7” (CAS: Column Address Strobe.) Clearly, the lower the number the better, as in order to access the requested data both the row and the column needs to be accessed.

RAS Precharge

Aka tRP

Example timing: 9-10-11-24-2

After a successful data retrieval from the memory, the row that was used to access the data needs to be closed. This needs to happen so that a new row can be accessed. RAS Precharge is the time between the command is issued to close the row, and a new row becoming available for use. This has a reduced effect on performance than that of CL.

Active to Precharge Delay

Aka tRAS

Example timing: 9-10-11-24-2

tRAS is simply the time the memory has to wait once it finishes a command before it can accept and act upon a new one. tRAS is the second biggest effect on performance, after CAS Latency.

Command Rate

Aka CR or CMD.

Example timing: 9-10-11-24-2

The time taken from the memory being activated to the possibility of an action being delivered to it. Whilst a topic of much debate, it is generally agreed that CR1 gives better performance, whilst CR2 gives potentially more stable overclocks. The performance difference is rather negligible (from personal testing thusfar), though I’m sure there are some that will disagree with me.

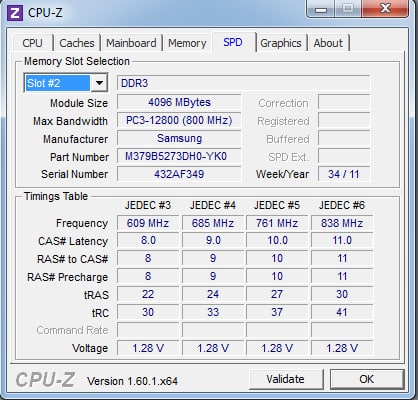

Remember, also, that DDR stands for Double Data Rate. So when you see memory screen shots of software like CPU-Z or AIDA64 that shows 2400Mhz RAM at 1200Mhz, or 1600Mhz RAM at 800Mhz.. double it. There you go, DDR explained.

There you have it. A breakdown of each memory timing in a manner that is hopefully easy to digest. To reiterate, when looking at memory timings, your priority should be CL and tRAS, then the others. Lower is always better, but don’t sacrifice CL or tRAS speeds for tRP or tRCD.

We hope this was helpful; feel free to discuss memory with us over at our forums!